## Last Time: Exceptions and Storage

- Construction of a pipelined datapath for Y86

- Exceptions

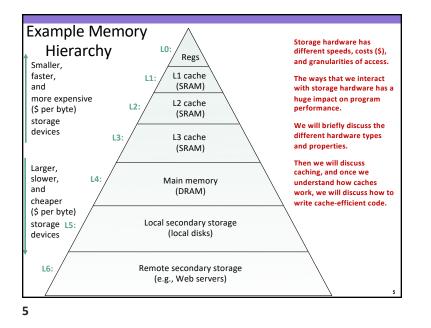

- Storage technologies and trends (Ch 6.1)

- Memory technologies

- Locality of reference (Ch 6.2)

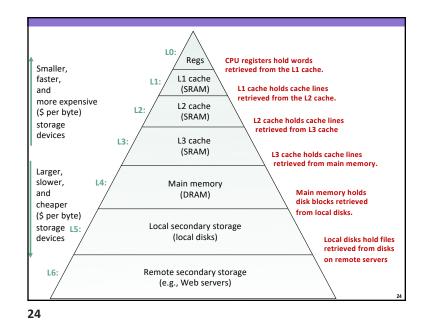

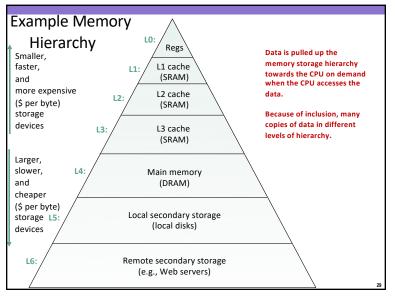

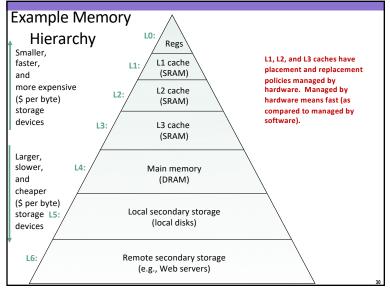

- The memory hierarchy (Ch 6.3)

## Administrative Details

- Read CSAPP 6.4-6.6

- Lab #5 checkpoint due Wednesday at 11pm

- Use getopt() to parse command line arguments

- Look at slides on lab assignment page for example uses of getopt()

- If you want to find a study buddy, please send me an email

2

# Today: Storage and Caches

- Storage technologies and trends (Ch 6.1)

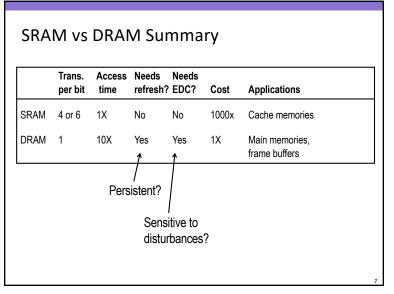

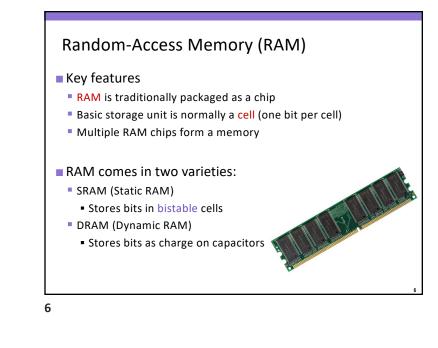

- Memory technologies

- Cache memory organization and operation (Ch 6.4)

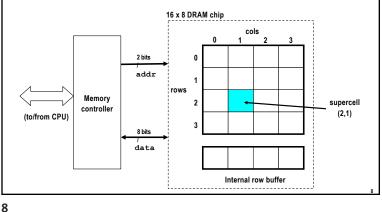

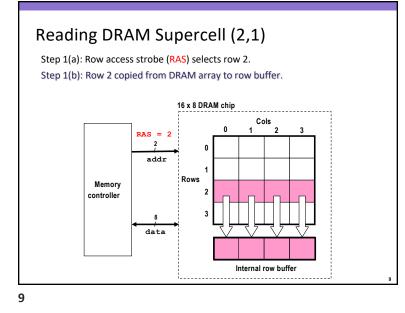

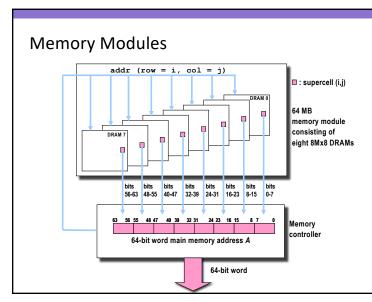

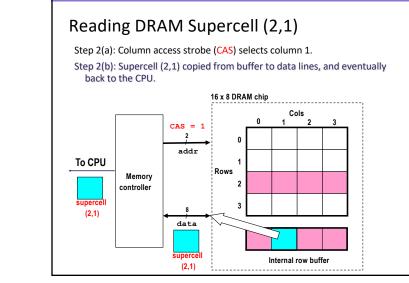

## Conventional DRAM Organization

#### d x w DRAM:

dw total bits organized as d supercells of size w bits

10

### **Enhanced DRAMs**

- Basic DRAM cell has not changed since its invention in 1966.

- Commercialized by Intel in 1970.

- DRAM cores with better interface logic and faster I/O:

- Synchronous DRAM (SDRAM)

- Uses a conventional clock signal instead of asynchronous control

- Allows reuse of the row addresses which leads to faster output rate

- Double data-rate synchronous DRAM (DDR SDRAM)

- Double edge clocking sends two bits per cycle per pin

- Different types distinguished by size of small prefetch buffer:

- DDR (2 bits), DDR2 (4 bits), DDR3 (8 bits)

- By 2010, standard for most server and desktop systems

- Intel Core i7 supports DDR3 and DDR4 (8 bits, but faster) SDRAM

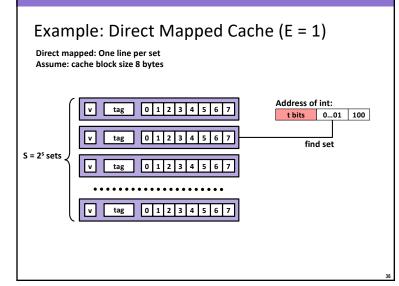

# General Caching Concepts: Types of Cache Misses

- Compulsory miss

- Compulsory misses occur because the cache is empty, or *cold*.

- Conflict miss

- Most caches limit blocks at level k+1 to a small subset (sometimes a singleton) of the block positions at level k.

- E.g. Block i at level k+1 must be placed in block (i mod 4) at level k.

- Conflict misses occur when the level k cache is large enough, but multiple data objects all map to the same level k block.

- E.g. Referencing blocks 0, 8, 0, 8, 0, 8, ... would miss every time

- Capacity miss

- Occurs when the set of active cache blocks (*working set*) is larger than the cache.

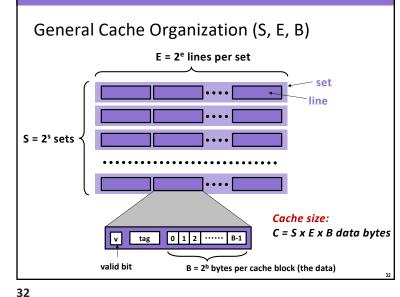

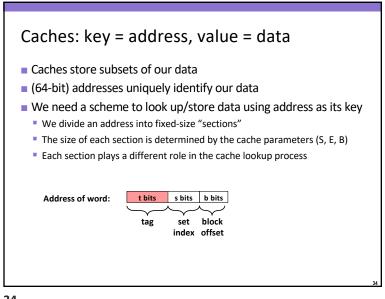

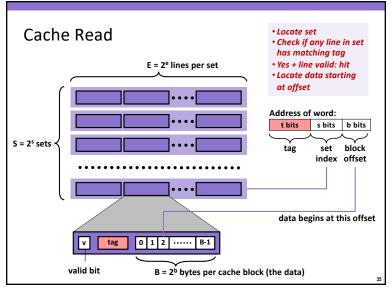

# **Cache Memories**

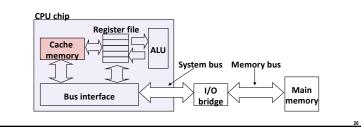

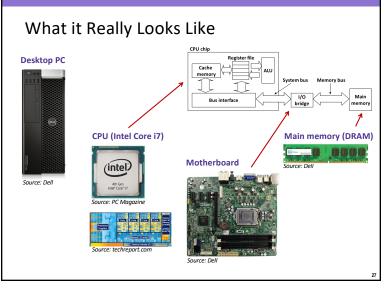

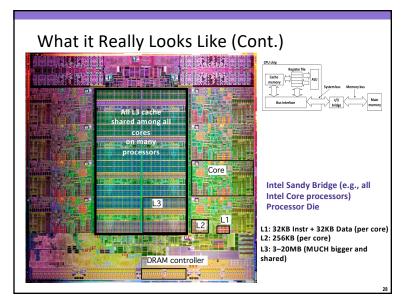

- Cache memories are small, fast SRAM-based memories managed automatically in hardware

- Hold frequently accessed blocks of main memory

- CPU looks first for data in cache

- Typical system structure:

## **Connection Between Locality and Cache**

- Blocks = spatial locality

- Retrieving and keeping in cache = temporal locality